# Programmable audio attenuator

Gain controlled line amplifier offers a 60 dB range in 1 dB steps

by J. M. Didden

After experimenting with various linear gain control systems, the author chose a combination of linear and logic circuits to provide a high quality audio attenuator. The final design uses a 6-bit word to program the gain, and can be used for remote control applications or, with the aid of a microprocessor, for automatic level

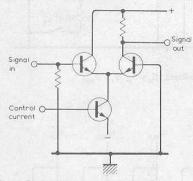

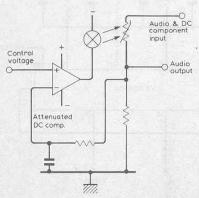

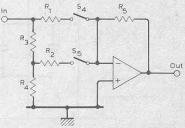

This circuit was originally designed to remotely control the volume and balance in a stereo system. Several methods were tried, such as the two-quadrant multiplier in Fig.1. However, this circuit suffered from high distortion for input levels of more than 100mV, and tracking between units was poor. Attempts to improve the performance with current-source loading did not significantly improve the performance. A f.e.t. used as a voltage controlled resistor produced similar problems, so a l.d.r. design was tried as shown in Fig.2.

Fig. 1 Basic two-quadrant multiplier.

Fig. 2 Closed-loop light dependent resistor attenuator.

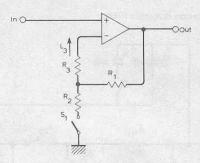

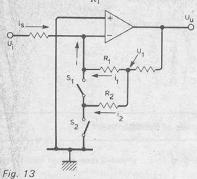

Fig. 3 Basic gain switching circuit.

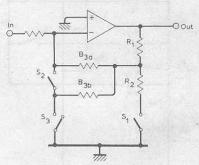

Fig. 4 Extended circuit with two independent switches.

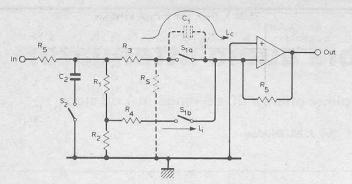

This circuit had a good signal level capability, and tracking between units was made almost perfect by using a compound audio plus d.c. input. The attenuated d.c. was fed back to the control circuit. Unfortunately, the l.d.r. produced high noise levels at medium to high attenuation, and control-loop stability was difficult to achieve. Because these analogue approaches did not produce the performance required, I investigated gain switching with f.e.ts. Although f.e.ts are nonlinear, this is not a problem if the signal voltage across a closed switch is very small. A basic circuit is shown in Fig.3. When f.e.t. S, is closed, the signal across it equals the input voltage times the ratio of the f.e.t. on resistance to R2. In practice, ratios of 1/1000 are easily obtained, so a signal level of several volts, which is not uncommon in a line amplifier, produces only a few millivolts across the switch. At these levels the f.e.t. is almost perfectly linear. Two independent gain settings can be achieved by switching  $R_3$  and keeping  $I_3$  constant. With  $S_2$ closed and  $S_3$  open in Fig.4,  $R_{3a}$  and  $R_{3i}$ are connected from R1 to the virtual

earth of the op-amp. With  $S_2$  open and  $S_3$  closed,  $R_{3b}$  is connected to the real earth. Therefore, by using a s.p.d.t. switch for  $S_2$   $S_3$ , and a s.p.s.t. for  $S_1$ , four gain settings are possible.

An extension of this circuit is shown in Fig. 5 where, with  $S_5$  closed and  $S_4$  open, gain is determined by the ratio of  $R_5$  to  $R_1$ . With  $S_5$  open and  $S_4$  closed, the gain is determined by the ratio of  $R_5$  to  $R_1$  and  $R_3$  to  $R_4$ . Combining the circuits in Fig. 4 and Fig. 5 gives eight gain settings. For all of these configurations the switches have only a small signal across their on resistance and carry very little current when opened. The values of the series resistors are high compared with the off resistance.

Selection of a suitable f.e.t. presented some problems. Switch arrays for analogue applications are available, but are generally expensive. Analogue multiplexers, such as the 4051, contain eight c.m.o.s. switches with a common input and integral one-of-eight decoder for control by a 3-bit word. However, the switching produces spikes on the audio output due to an internal capacitive coupling of the control signal to the switch terminals. This can be minimised by loading the switch, but smaller resistors must then be used which consequently produces higher distortion levels. Although "soft" switching with a RC network is one solution, see Fig. 6,

Fig. 5 Alternative two-switch circuit

Fig. 6 Soft switching to overcome spikes

Fig. 7 Internal capacitance effect and compensation low-pass filter.

the gate of the f.e.t. must be accessible. I finally decided to use the low cost 4007 which contains two s.p.d.t. switches and an inverter.

In practice, 1dB steps in gain produce a gradual change and a range of about 60dB is sufficient for most applications. Because high value series resistors are required, high attenuation can only be achieved with the circuit in Fig. 5. However, as shown in Fig. 7, if  $S_{1b}$  is closed and  $S_{1a}$  is open, a small current flows through the internal switch capacitance. At high attenuation and high signal frequencies, this current may not be insignificant and can cause an output that rises with frequency.

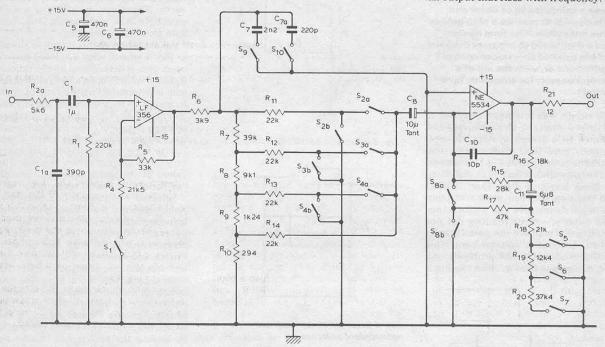

Fig. 8 Complete attenuator circuit for one channel. The switches are grouped in five i.cs as follows;  $S_5 + S_{g'} S_7 + S_{8ab'_1} S_{2ab} + S_{3ab'} S_{4ab} + S_7$  and  $S_9 + S_{10'}$ . All resistors should be 1%.

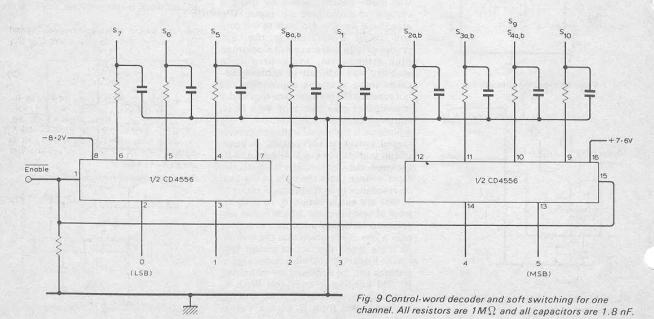

This problem can be overcome by grounding the left terminal of S1 when it is open, and this is easily achieved with the 4007 s.p.d.t. switches. Because there is an on resistance, R<sub>s</sub>, a small signal voltage remains across the open switch. The low-pass filter R<sub>5</sub> C<sub>2</sub> compensates for this with S2 closed when S1b is closed and S1a is open. The frequency response is flat within 0.3 dB up to 25 kHz and at high attenuation. Fig. 8 shows the final circuit for one channel and table 1 shows the range of attenuation levels. Ten mixed s.p.s.t. and s.p.d.t. switches are required and these can be produced with five 4007 i.cs. It is important that the signal amplitudes across S1, S8, S5, S6 and S7 do not exceed the positive or negative supply voltages because an internal protection diode will conduct and cause distortion. As audio signals are bipolar, the supply voltage should be centered around ground because one side of the open switches is always connected to either a signal ground or virtual earth. To balance the on resistances of the p and n-channel m.o.s.f.e.ts, a positive supply of 7.6V and a negative supply of 8.2V is used. In Fig. 8, S, and S<sub>8a,b</sub> can be controlled by a single bit. Switches S2a to S4b and S5 to S7 require the four decoded values of a 2-bit control word. This is carried out by a 4556, which containes two one-of-four decoders, see Fig. 9.

Selection of the switch-network resistors is a compromise as already explained. The typical on resistance of a switch is about  $300\Omega$  and the maximum variation is about  $200\Omega$ . With a series resistor of  $22k\Omega$  1%, this is comparable with the switch tolerance. Calculations for the resistor values are given in the appendix. Fig. 8 also shows that some switches are capacitor-coupled to the circuit by  $C_8$  and  $C_{11}$ . These remove a small output offset-voltage change with gain which can be

Fig. 10 Inverting input buffer.

Fig. 11 Alternative compensation networks for other op-amps.

| Attenuation | Table 1. Gain and switch settings |                 |          |          |          |                 |                 |                |                |                |                 |                 |

|-------------|-----------------------------------|-----------------|----------|----------|----------|-----------------|-----------------|----------------|----------------|----------------|-----------------|-----------------|

| steps dB    | $S_1$                             | S <sub>2a</sub> | $S_{2b}$ | $S_{3a}$ | $S_{3b}$ | S <sub>4a</sub> | S <sub>4b</sub> | S <sub>5</sub> | S <sub>6</sub> | S <sub>7</sub> | S <sub>8a</sub> | S <sub>8b</sub> |

| 0           |                                   |                 |          |          |          |                 |                 | С              | 0              | 0              |                 |                 |

| 1           |                                   |                 |          |          |          |                 |                 | 0              | C              | 0              |                 |                 |

| 1 2 3       |                                   |                 |          |          |          |                 |                 | 0              | 0              | C              |                 |                 |

| 3           |                                   |                 |          |          |          |                 |                 | 0              | 0              | 0              |                 |                 |

| 0           |                                   |                 |          |          |          |                 |                 |                |                |                | 0               | C               |

| 4           |                                   |                 |          |          |          |                 |                 |                |                |                | C               | 0               |

| 0           | С                                 |                 |          |          |          |                 |                 |                |                |                |                 |                 |

| 0           | O                                 |                 |          |          |          |                 |                 |                |                |                |                 |                 |

| 0           |                                   | С               | 0        | 0        | C        | 0               | C               |                |                |                |                 |                 |

| 16          |                                   | O               | C        | Č        | O        | 0               | C               |                |                |                |                 |                 |

| 32          |                                   | 0               | C        | 0        | C        | C               | 0               |                |                |                |                 |                 |

| 48          |                                   | 0               | C        | 0        | C        | 0               | C               |                |                |                |                 |                 |

Table 2. Performance details of the attenuator

Max. r.m.s. output level Max. input level Max. capacitive load

Max, capacitive load Frequency response Output noise level T.h.d. and i.m. Gain 8.5V across 600Ω.

3.8V or 9V depending on S<sub>1</sub>, provided max. output level is not exceeded.

10 nF,

better than 10 Hz to 25 kHz within 1 dB.

at least 86 dB below 1 V r.m.s. at all gain settings (unweighted). less than 0.03% and 0.02% respectively.

variable in 1 dB steps from 16.8 dB to -46.2 dB.

heard as clicks at low input signal levels.

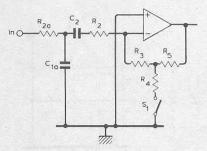

The capacitor values have been chosen to give a low-frequency response to below 10Hz. A f.e.t. input opamp, LF 356, is used to provide a high input impedance, wide bandwidth, high slew-rate and low distortion. A NE 5534 is used at the output because it can deliver a high output level into a 6000 load with little distortion. With R<sub>21</sub> and C<sub>10</sub> to stabilize the op-amp, a 10nF load will not produce ringing or overshoot of a square-wave signal. The 5534 is also a low noise device, which is important, because most of the attenuation takes place at its input and this reduces the

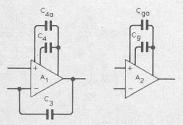

signal-to-noise ratio of the last stage. Performance parameters of the complete amplifier are shown in table 2. If a f.e.t. input selector switch is required, the LF 350 can be used in the inverting mode as shown in Fig. 10. The compensation capacitors, which may be necessary with other op-amps, are shown in Fig. 11.

If a visual indication of the attenuation is required, the control word can be converted to a two-digit b.c.d. output for driving a seven segment display.

To be continued

### **Appendix**

#### Calculation of resistor values.

For these calculations a dB table or calculator with log, and inverse log, functions is re-

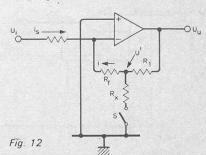

For the 1, 2 and 3 dB attenuators in Fig. 12, with S open,

$$i = \frac{U_{u1}}{R_1 + R_f} \tag{1}$$

for an output of  $U_{u1}$  volts. With S closed and an output of  $U_{u2}$  volts, the equivalent voltage source  $U_1$  is

$$U_{u2} \frac{R_{x}}{R_{x} + R} \tag{2}$$

and the equivalent source resistor is

$$\frac{R_1 R_{\rm x}}{R_1 + R_{\rm x}} \tag{3}$$

therefore.

$$i = U_{u2} \frac{R_{x}(R_{1} + R_{t})}{R_{I}R_{x} + R_{f}(R_{1} + R_{x})}$$

(4)

Because i always equals  $i_{\rm s}$ , equations (1) and (4) are equal. Substituting G for  $U_{\rm u2}/U_{\rm u1}$  gives

$$R_{x} = \frac{R_{1}R_{f}}{(G-1)R_{1} + R_{f}}$$

(5)

The minimum resistor values for  $R_1$  and  $R_f$ , for a given G and  $R_x$ , are obtained if  $R_f = R_f$ . The minimum  $R_x$  is found for G = 3 dB and, taking  $R_x = 20 \mathrm{k}\Omega$  as a design value,  $R_1$  and  $R_x$  are about  $18 \mathrm{k}\Omega$ . However,  $R_f$  is also part of the 4dB network, so this is calculated first using a  $R_f$  of  $18 \mathrm{k}\Omega$ .

The circuit is given in Fig. 13. If S<sub>1</sub> is closed and S2 is open,

$$i = \frac{U_1}{R_1} + \frac{U_1}{R_2} \tag{6}$$

With S1 open and S2 closed,

$$i = \frac{U_1}{R_{\rm T}} \tag{7}$$

As already mentioned,  $i_1$ ,  $i_2$  and  $U_1$  are equal in both cases. In the first case, gain is the ratio of  $i_s$  to  $i_1+i_2$ , and in the second case, the ratio of  $i_s$  to  $i_1$ . The change in gain is there-

$$G = \frac{i_1 + i_2}{i_1} \tag{8}$$

and equations (6), (7) and (8) give

$$R_1 = R_2(G-1)$$

(9)

$$R_2 = \frac{R_1}{G_{-1}}$$

(10)

Substituting  $R_1//R_2 = 18 \mathrm{k}\Omega$  in (10) gives

$$R_2 = \frac{G.18k\Omega}{G-1} \tag{11}$$

For G=4dB,  $R_2$  is about  $48\text{k}\Omega$ . Using the standard value of  $47\text{k}\Omega$  and adding the nominal on resistance of the switch gives  $47.3k\Omega$  and  $R_1$  becomes  $27.6k\Omega$ . With the nearest preferred values,  $R_{15}$  is  $47k\Omega$  and  $R_{17}$ is  $28k\Omega$  in Fig. 8.

The value of  $R_f$  in (5) now becomes 17.46 k $\Omega$ ,

i.e.  $R_1//R_2$ . The  $R_\infty$  values are calculated next. For G=1 dB,  $R_\infty$  is 72.64 k $\Omega$ , which is the on resistance in Fig. 8. For G=2 dB,  $R_\infty$  is 34.23 k $\Omega$ which is  $R_{18} + R_{19} +$  on resistance. For G = 3 dB,  $R_x$  is 21.48 k $\Omega$ , i.e.  $R_{18} +$  on resistance. With the nearest preferred value,  $R_{18}$  is 21 k $\Omega$ ,  $R_{19}$  is 12.4

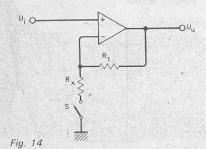

k $\Omega$  and  $R_{20}$  is 37.4 k $\Omega$ . For the 8 dB switch refer to Fig. 14. With S open the gain is 0 dB, and with S closed the gain is  $R_1 + R_x/R_x$  which gives

(12)

Choosing 33 k $\Omega$  for  $R_1$  gives 21.83 k $\Omega$  for  $R_8$ . Subtracting the 300 $\Omega$  on resistance gives a standard value for  $R_4$  in Fig. 8 of 21.5 k $\Omega$  and 33

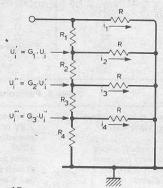

Calculations for the remaining switch network are more difficult because the series resistors are either connected to ground or to virtual earth, see the equivalent circuit in Fig. 15. To save a switch, R<sub>14</sub> in Fig. 8 always

Fig. 15

delivers current to the summing node. Therefore, for the various gain settings, the following input currents flow;

No attenuation,  $i_1 + i_4$

$-16 \text{ dB}, i_2 + i_4$

$-32 \text{ dB}, i_3 + i_4$ -48 dB, i

For a gain step A, the current ratios are

$$A = \frac{i_2 + i_y}{i_1 + i_y} \tag{13}$$

$$A = \frac{i_3 + i_y}{i_2 + i_y} \tag{14}$$

$$A = \frac{i_{y}}{i_{3} + i_{y}} \tag{15}$$

If all series resistors are equal, gain changes only depend on voltages  $G_1U_i$ ,  $G_2U_i$  and  $G_3U_i$ . Therefore,

$$G_1 = \frac{i_2}{i_1}$$

(16)

$$G_2 = \frac{i_3}{i_2}$$

(17)

$$G_3 = \frac{i_4}{i_2}$$

(18)

If A is -16dB,

$$G_3 = \frac{A}{1 - A} (0.188 - 14.5 dB) \tag{19}$$

$$G_2 = \frac{A}{1+A}(0.137-17.3\text{dB}) \tag{20}$$

$$G_1 = \frac{A}{1 + \frac{A^2}{1 + A}} (0.155 - 16.2 dB)$$

(21)

Note that A is the input-current gain step and  $G_n$  is the gain step of the voltage across the series resistor relative to  $G_n-1$ .

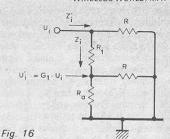

In the simplified circuit of Fig. 16, because  $Z_i^1 = Z_i / / R,$

$$Z_{i} = \frac{Z_{i}^{1} R}{R - Z_{i}^{1}}$$

(22)

and

$$R_1 = Z_i \frac{R \cdot R_a}{R + R} \tag{23}$$

also, because

$$G_1 = \frac{\frac{R \cdot R_a}{R + R_a}}{Z_i}$$

$$G_1 Z_1 = \frac{R \cdot R_a}{R + R}$$

Therefore,

$$R_1 = Z_1(1 - G_1) \tag{24}$$

and

$$R_{\rm a} = \frac{R \cdot G_1 \cdot Z_{\rm i}}{R - G_1 \cdot Z_{\rm i}} \tag{25}$$

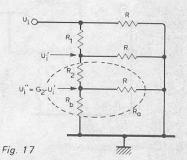

Again, using a design value of  $22k\Omega$  for the series resistors, and adding  $300\Omega$  on resistance gives 22.3 k $\Omega$  for each resistor. As  $R_{14}$  in Fig. 8 has no series switch, R in formula (30) and on will be  $22 k\Omega$ . After a little trial-and-error to find a standard value for  $R_1$ , the value of  $Z_1^1$  was set to 15.04 kΩ, which is the constant load presented to the buffer amplifier. From (22), (23) and (24),  $Z_i$  is 41.2 k $\Omega$  and  $R_1$  is 39 k $\Omega$ . From (25),  $R_a$  is 10.55 k $\Omega$ . By repeating this procedure Fig. 17 is achieved where

$R_2 = R_a - \frac{R \cdot R_b}{R + R_b}$ (26)

$$G_2 = \frac{R \cdot R_b}{R + R_b} \tag{27}$$

burst of 3, making a total of 43 (including the no-error case). The first cyclic burst-error-correcting codes, due to P. Fire, needed 3b - 1 check digits for bursts of length up to b, but later codes listed by Lucky, Salz and Weldon7 are better. Peterson and Weldon quote on p.364 a code length 15 capable of correcting bursts up to length 3 with only 6 check digits, as against 10 or 3 random errors. In fact the rule is that a code capable of detecting bursts up to length b needs precisely b check digits but a code for correcting such bursts needs at least 2b check digits. Codes using exactly 2b check digits are known for lengths 7, 15, 27, 34 and 50 with corresponding values of b of 2, 3, 5, 6 and 8; and a few more check digits are required for longer codes. (But the longer codes cited by Peterson and Weldonhave mostly fairly small values of b, between 3 and 7).

The mathematical techniques used in the construction of these cyclic burst-error-correcting codes are very similar to those of the BCH codes. For example the (15,9,3b) code for correcting bursts up to length 3 can be constructed from the pattern

111100100000000

which is taken to be  $2^8$ , and its 8 right shifts which are taken to be the powers of two from  $2^7$  to  $2^0 = 1$ . Then the decimal number 409, which is  $2^8 + 2^7 + 2^4 + 2^3 + 2^0$ , encodes as

100000110100001

There may be a requirement to correct both random and burst errors. It is often said that random errors are typical of radio communication, as a result of thermal and shot noise in the receiver and atmospherics; but bursts are typical of land-line circuits, as a

result of intermittent contacts in switching systems or interference from power lines. But clearly this is an oversimplification, particularly as land lines are using higher and higher trequencies, to say nothing of wave guides and optical fibres. Then one device to avoid special measures for the correction of burst errors as well as random errors is to scramble the order of digits before transmission and unscramble them at the receiver. The re-ordering of digits at the receiver will break up any bursts into scattered errors which can be dealt with by a code for random errors. However, the whole point of burst-errorcorrecting codes is that for a given number of check digits they can deal with more errors in a burst than scattered at random; so the scrambling should extend over more than one block so that, for example, a burst of 6 errors in one block length during transmission becomes 3 random errors in each of two blocks after "unscrambling" in the receiver.

Error-correcting and error-detecting codes constitute a vast subject, with special codes being developed for special purposes. This article makes no, pretence of reviewing the subject: it aims merely to explain some of the underlying principles with illustrative examples. The subject is formidably mathematical, so that most users will be content to use existing codes rather than attempt to design codes for themselves; but even to list all existing codes with their properties would be a very major undertaking. Most of them can be found in books such as Peterson and Weldon4 but there are always a few which have been developed since the publication of a book. Fortunately the

basic codes such as BCH will serve for most purposes.

Appendix. The Golay code

Golay discovered a triple-errorcorrecting binary code of length 23, with 12 information digits, which is perfectly packed. A code of length n=23and capable of correcting up to 3 random errors will have to be able to distinguish between  $1 + 23 + {2 \choose 2} + {2 \choose 3}$  error patterns. The binomial coefficients evaluate to 253 and 1771 so that the whole series sums to 2048, which is exactly 211; and so with 11 check digits (and therefore 12 information digits) the code is perfectly packed. This Golay (23,12,3) code is the only binary code capable of correcting more than one error which is perfectly packed. A cyclic code which is equivalent to the Golay code can be developed from the following sequence and its eleven shifts:-101011100011000000000000

#### References

- Hamming, R. W., Error detecting and error correcting codes. Bell Syst. Tech. J., vol. 29, pp 147-160 (1960)

- Golay, M. J., Notes on digital coding. Proc. Inst. Rad. Engr., vol. 37 p.657 (1949)

- Tietäväinen, A., On the nonexistence of perfect codes over finite fields. SIAM J. Appl. Math., vol. 24 pp 88-96 (1973)

- Peterson, W. W. and Weldon, E. J., Error Correcting Codes. The M.I.T. Press (Cambridge, Massachussets, 1972)

- Bell, D.A. and Laxton, R., Some BCH codes are optimum. Electronics Letters, vol. 11 pp 296-297 (1975)

- Hsiao, M.Y., Bossem, D.C. and Chiem, R. T. Orthogonal Latin square codes. I. B. M. Journ. R&D, vol. 14, pp 390-394 (1970)

- Journ. R&D, vol. 14, pp 390-394 (1970)

7. Lucky, R. W., Salz. J. and Weldon, E. J.

Principles of Data Communication,

McGraw Hill (New York, 1968)

## Programmable audio attenuator

From this

$$R_2 = R_a(1 - G_2)$$

(28)

and

$$R_{b} = \frac{G_{2}R_{a}R}{R - G_{2}R_{a}}$$

(29)

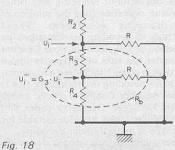

Therefore,  $R_2$  is  $9.09~k\Omega$  (9.1  $k\Omega$  standard value) and  $R_b$  is  $1.54~k\Omega$ . The last step gives Fig. 18 where

$$R_3 = R_b - \frac{R \cdot R_y}{R + R_y} \tag{30}$$

and

$$G_3 = \frac{R \cdot R_y}{R + R_y} \tag{31}$$

From (30) and (31),

$$R_3 = R_b(1-G_3)$$

$R_y = \frac{G_3 \cdot R_b \cdot R}{R_s \cdot G_s \cdot R_b}$

and  $R_{y} = \frac{G_3 \cdot R_{b} \cdot R}{R \cdot G_3 \cdot R_{b}}$

The nearest standard value for  $R_3$  is  $1.24~\mathrm{k}\Omega$  and for  $R_4$  is  $294\Omega$ . These calculations give an idea of the accuracy that can be expected. The worst case error occurs with a maximum

error in the input switching network of  $A_2$ . If, for example,  $R_{\rm H}$  and  $S_{\rm 2a}$  in Fig. 8 each have a maximum resistance error of  $200\Omega$  in the same direction, the gain error would be no more than 0.15 dB.

#### \* Printed circuit board

A printed circuit board which accommodates one attenuator circuit and decoder will be available for £4.20 inclusive of v.a.t. and UK postage from M. R. Sagin at 23 Keyes Road, London NW2.

#### The author

J. M. Didden started his career in 1964 with Philips where he was involved in the design of tv receiver deflection circuits. After three years he joined the Royal Netherlands Air Force to work in air defence operations and specialise in software.

The author is currently involved with software design for NATO air defence systems. Apart from audio, his hobbies include reading science fiction.